北理工課題組在光量子邏輯門研究方面取得重要進展

發布日期:2023-05-29 供稿:物理學院 攝影:物理學院

編輯:王莉蓉 審核:陳珂 閱讀次數:

日前,北京理工大學物理學院張向東教授課題組與清華大學電子工程系黃翊東教授課題組張巍教授開展合作,基于反設計方法,實驗實現了目前世界上最小的光量子邏輯門。相關成果以“Super-compact universal quantum logic gates with inverse-designed elements”為題發表在Science Advances期刊[Science Advances, 9, adg6685]上。該工作得到了國家自然科學基金委和國家重點研發計劃的大力支持。北京理工大學物理學院博士生何路、清華大學電子工程系博士生劉東寧為該論文的共同第一作者,北京理工大學物理學院張向東教授、清華大學電子工程系張巍教授為論文共同通訊作者。另外,北京理工大學張慧珍副研究員、張蔚暄研究員;清華大學劉仿教授、馮雪副教授、崔開宇副教授、學生高景行也對此工作做出了貢獻。

實現通用量子計算機是量子信息科學領域的重要目標。理論上,級聯一定數量的基礎量子門可以實現通用量子計算機。基于此,級聯控制非(CNOT)門和單比特量子門的量子光子集成回路已被廣泛認為是實現大規模量子信息處理的有前途的技術。近年的工作中,人們利用多層邁克曾德爾干涉儀(MZI)成功構造了可以實現任意雙量子比特處理的硅光子量子回路,但它的尺寸在毫米量級。對于數十量子比特的量子計算任務,芯片的整體尺寸需要達到晶圓級別大小。這不但對刻蝕工藝要求極高,而且也限制了芯片的使用。縮小量子邏輯門的尺寸是解決這一問題的關鍵。實現超緊湊的量子邏輯門是在較小的芯片尺寸下實現大規模量子計算的基礎。

另一方面,在緊湊的光電子器件設計中,反設計(inverse design)方法已經顯示了巨大優勢。人們利用這一方法設計出了許多基本光學元件。這些反設計的器件具有比傳統設計方法更好的性能和更緊湊的結構。但目前這些研究都專注于經典電磁波系統中的器件設計。例如,北理工研究團隊通過使用拓撲優化方法(反設計方法中的一種),在SOI基片上曾設計并制備了目前世界最小的經典介電全光邏輯門(ACS Photonics 9, 597-604)。然而,對于光量子芯片領域,反設計方法尚未引入。這就自然產生了一個重要問題:當反設計方法應用于芯片上量子邏輯器件的設計時,是否可以做到更小的尺寸和更少的損耗?

本工作中,研究人員使用反設計方法在源集成的硅光子芯片上設計并制備出了超緊湊的通用量子邏輯門(依托天津華慧芯科技高端光電子研發工藝代工平臺)。進一步,通過級聯多個CNOT門和單比特量子門,研究人員也討論了任意光量子回路的進一步擴展方法。

研究亮點之一:基于反設計方法的超緊湊單比特量子門

研究人員將量子門及輔助測試系統制備在頂硅厚度為220nm厚的SOI平臺上。如圖1a所示,該量子芯片由四個模塊組成,分別是:(I)量子源,(II)態制備,(III)量子門和(IV)態層析模塊。本研究主要關注通過反設計方法制備的超緊湊量子門,包括Hadamard門、相位z門以及CNOT門,分別如圖1b-1d所示。

圖1. 超緊湊量子邏輯器件及測試系統示意圖

測試這些量子門的實驗裝置如圖1e所示。在模塊I中,通過片上的自發四波混頻過程激發同頻的兩個光子,并在模塊II中將其編碼到兩個任意路徑編碼的疊加態中,為測試量子門做好準備。然后,將路徑編碼的量子比特注入到反設計的量子門中(模塊III)。輸出的量子比特通過態層析的第四個模塊進行投影和檢測。輸出的量子態通過一維光柵耦合到光纖中,并通過光纖耦合的超導納米線單光子探測器(SNSPD)進行檢測。

研究人員首先設計了單比特Hadamard 門。一般來說,在光量子芯片上,需要使用50:50的分束器(BS)來實現 Hadamard 門,其中輸入量子態![]() (來自輸入端口 a in )被轉化為疊加態

(來自輸入端口 a in )被轉化為疊加態![]() 。這里 c1(c2)表示在端口 a out ( b out )的輸出態

。這里 c1(c2)表示在端口 a out ( b out )的輸出態![]() (

(![]() )的系數。為了進行優化過程,研究人員首先定義一個與單光子激發有關的BS目標函數

)的系數。為了進行優化過程,研究人員首先定義一個與單光子激發有關的BS目標函數![]() 。在設計過程中,隨著目標函數被逐漸最大化,就可以得到優化后的結構。這個過程可以用下面的方程來描述:

。在設計過程中,隨著目標函數被逐漸最大化,就可以得到優化后的結構。這個過程可以用下面的方程來描述:

![]() (1)

(1)

其中,![]() 是設計場,它表示介電常數的材料分布(在空氣和Si之間),λ是波長,總目標函數是三個不同波長(λ=1520nm、1550nm和1580nm)下的目標函數之和,這是為了擴展器件工作頻率的范圍。此外,還應添加附加條件,即

是設計場,它表示介電常數的材料分布(在空氣和Si之間),λ是波長,總目標函數是三個不同波長(λ=1520nm、1550nm和1580nm)下的目標函數之和,這是為了擴展器件工作頻率的范圍。此外,還應添加附加條件,即![]() ,這可以使兩個端口的輸出量子態的振幅平方幾乎相同,從而實現50:50的分束比。

,這可以使兩個端口的輸出量子態的振幅平方幾乎相同,從而實現50:50的分束比。

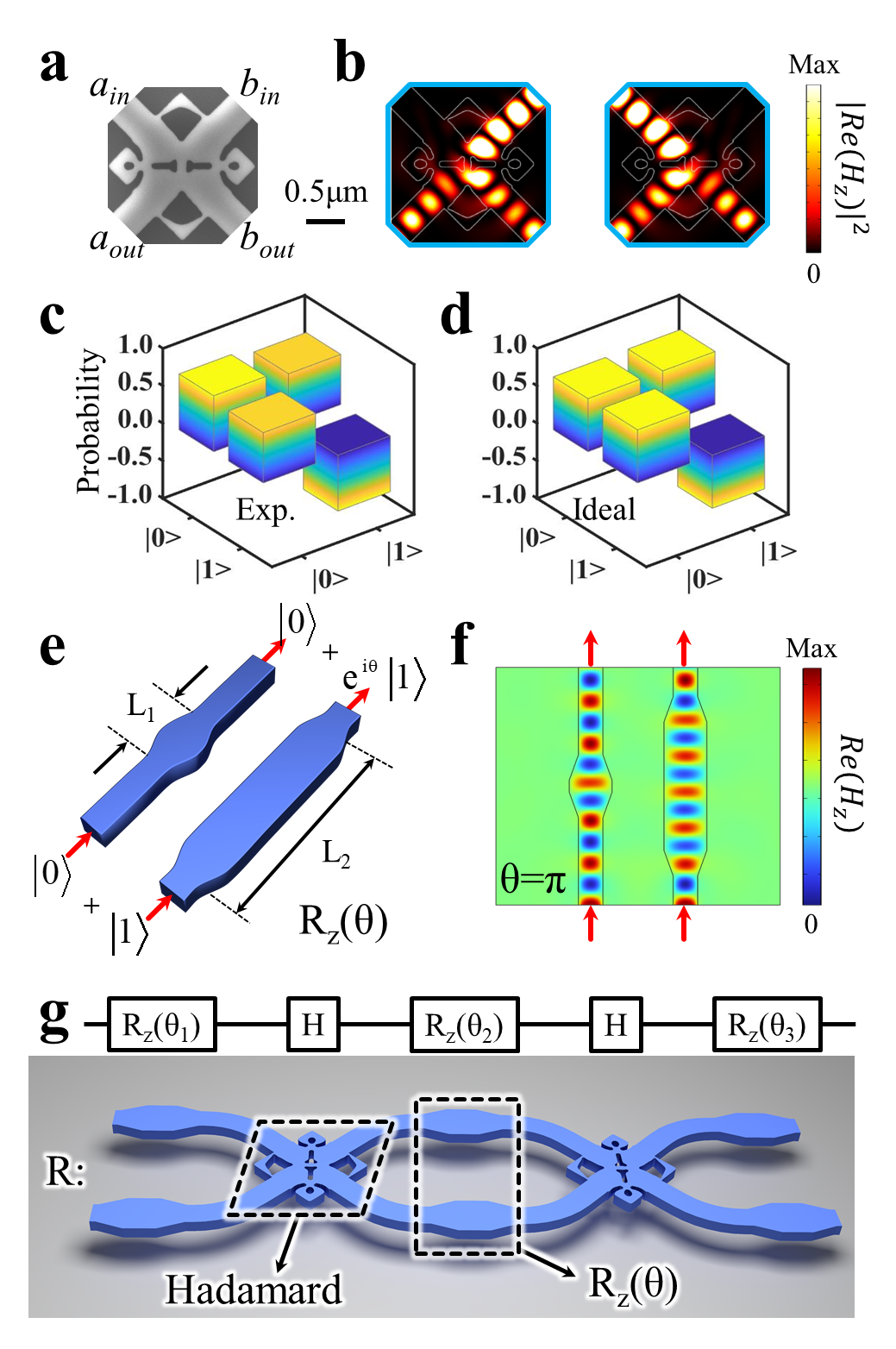

優化后的門通過電子束光刻和干法刻蝕制造,其SEM圖像如圖2a所示。它包含四個400nm寬的波導(分別命名為 a in 、 b in 、 a out 和 b out )和一個反設計的結構。該結構的尺寸僅為1.69μm2(1.3μm×1.3μm),小于一個真空波長。相比之下,先前的研究報道,基于定向耦合器或MMI制造的Hadamard門的尺寸約為102~103μm2,這意味著與以前的工作相比,該門的尺寸縮小了2~3個數量級。

基于單光子干涉原理,在設計的結構中可以執行Hadamard操作。當單光子態被注入到波導 a in 或 b in 中時,經過Hadamard門后,會轉化為在 a out 和 b out 處輸出的疊加態,并且具有π/2相位差。圖2b顯示了在a in 或b in 處單光子激發下的場分布的模擬結果,表明反設計的結構具有低損耗的50:50分束器的良好性能。

圖2. 反設計的單比特量子門。

為了測試這樣的結構是否能夠執行Hadamard門的功能,研究人員對該門進行了單量子比特層析實驗,如圖2c所示。可以清楚地看到,輸入態![]() 和

和![]() 成功地被轉化為

成功地被轉化為![]() 和

和![]() 。通過定量地表征Hadamard門,研究人員還計算了其保真度FH為0.987(3)。高的保真度進一步表明,Hadamard門的功能被成功實現了。

。通過定量地表征Hadamard門,研究人員還計算了其保真度FH為0.987(3)。高的保真度進一步表明,Hadamard門的功能被成功實現了。

基于這樣的Hadamard門,結合相位旋轉z門Rz(θ),研究人員構建了任意的單比特量子門R。對于路徑編碼方案,研究人員通過在光量子態的兩條路徑之間引入相位差輕松實現Rz(θ)門。如圖2e所示,相位z門是由寬度為700nm、長度為L1和L2的加寬波導構成的。當L1≠L2時,在這些波導中的量子態![]() 或

或![]() 之間存在相位差θ。因此,相位z門可以實現。為了進一步表征Rz(θ)的性能,研究人員模擬了一個特殊情況(相位θ=π),并在圖2f中展示了場分布。模擬結果表明,相位z門具有極低的損耗和精確的相位π,可以附加到量子態

之間存在相位差θ。因此,相位z門可以實現。為了進一步表征Rz(θ)的性能,研究人員模擬了一個特殊情況(相位θ=π),并在圖2f中展示了場分布。模擬結果表明,相位z門具有極低的損耗和精確的相位π,可以附加到量子態![]() 上。然后,通過組合三個Rz門和兩個Hadamard門,可以構造任意單比特量子門R,如圖2g所示。三個Rz的相位分別為θ1、θ2和θ3,可以調整到任意的固定值。它可以將單量子比特態映射到布洛赫球上的任意點。

上。然后,通過組合三個Rz門和兩個Hadamard門,可以構造任意單比特量子門R,如圖2g所示。三個Rz的相位分別為θ1、θ2和θ3,可以調整到任意的固定值。它可以將單量子比特態映射到布洛赫球上的任意點。

研究亮點之二:基于反設計方法的超緊湊兩比特量子門

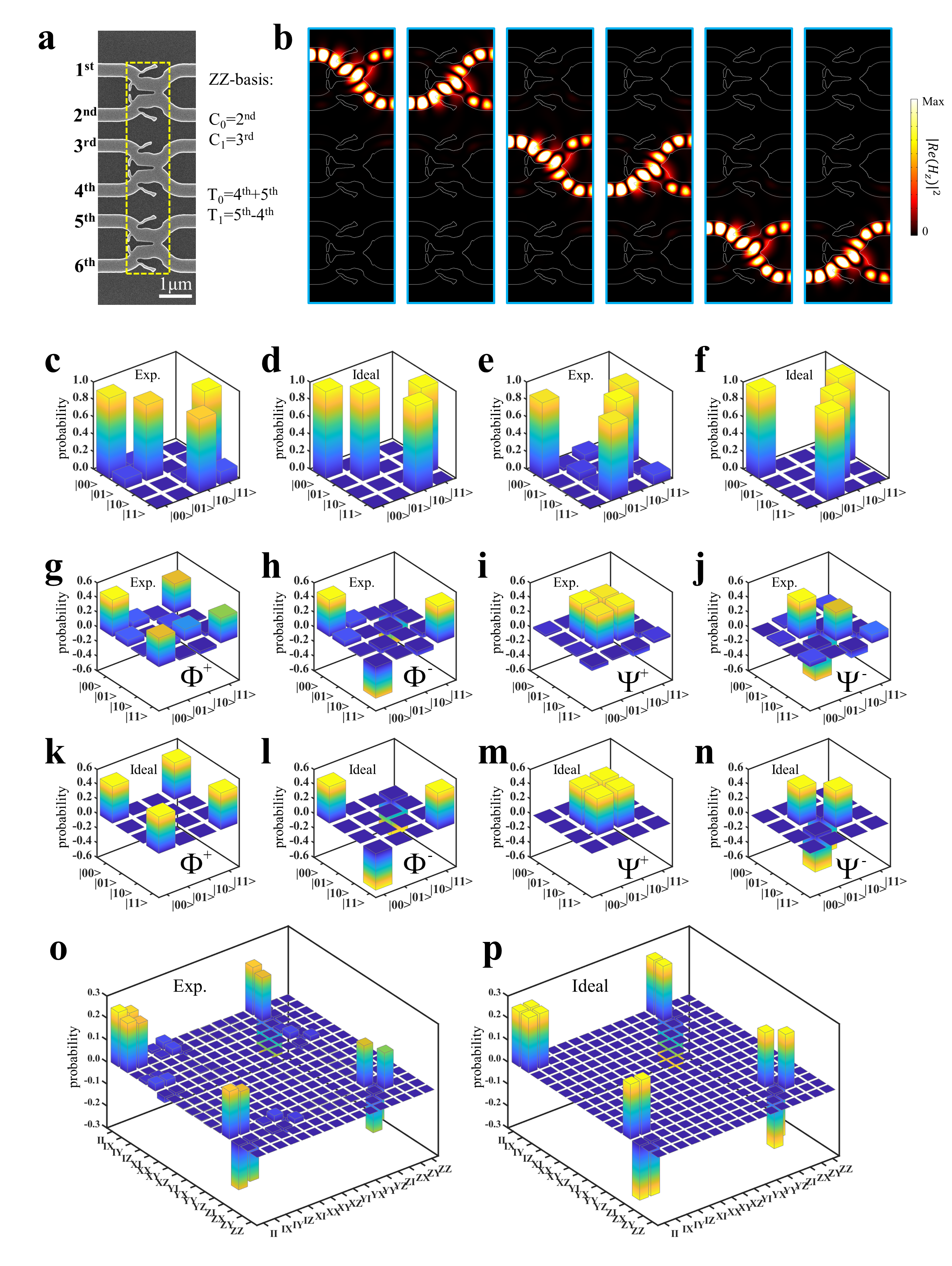

研究人員使用線性光學方案結合反設計方法,設計并制備了兩量子比特CNOT門。這種方案已在自由空間和集成光學中得到證明。CNOT門的設計可以通過將三個33:67分束器(透射率為T=0.67,反射率為R=0.33)并聯實現。因此,對CNOT門的反設計就是對33:67分束器的反設計。33:67分束器的反設計過程類似于Hadamard門,但需要更改設計過程中的優化參數。所設計和制作的CNOT門如圖3a所示。CNOT門的制作過程也類似于Hadamard門。33:67分束器之間的距離為500nm,以確保其中的量子態不會相互影響。CNOT門的寬度為6.4μm,深度為1.3μm(小于一個真空波長)在量子態傳播的方向上。據研究人員所知,這里設計的CNOT門的尺寸(8.32μm2)是目前世界上最小的。

圖3. 反設計CNOT門及其實驗結果和理論結果。

在設計的CNOT門中,有六個輸入和輸出波導,從上到下依次命名為第1到第6條波導。為方便起見,這些輸入波導中的量子態被定義為![]() 、

、![]() 、

、![]() 、

、![]() 、

、![]() 和

和![]() 。圖3b顯示了當這些單光子態(λ=1550nm)分別注入波導時的模擬場分布。可以看到,該器件具有良好的性能,可實現33:67分束器的功能,并且其損耗小,彼此之間沒有串擾耦合。

。圖3b顯示了當這些單光子態(λ=1550nm)分別注入波導時的模擬場分布。可以看到,該器件具有良好的性能,可實現33:67分束器的功能,并且其損耗小,彼此之間沒有串擾耦合。

為了實現CNOT門的功能,研究人員首先考慮在ZZ基下測量CNOT門功能。為了表征CNOT門的性能,研究人員測量了每個輸入態的輸出概率。在圖3c中,對所有輸入態,研究人員測量了投影到不同輸出態的符合計數,并對其進行歸一化處理,得到輸入輸出概率。相應的理論結果顯示在圖3d中。通過比較兩者,可以發現實驗結果與理論吻合良好。此外,通過計算,可以得到CNOT門的保真度為FZZ=0.9481±0.0064。接下來,研究人員還測試了該門在XX基下的邏輯功能。實驗結果(圖3e)與理論(圖3f)數據吻合良好。另外,研究人員也計算了XX基下的平均變換保真度Fxx=0.9445±0.0051。在ZZ和XX基下的高保真度定量地證明了該門實現了量子CNOT功能。

CNOT 門的一個重要功能是可以將兩個量子態糾纏在一起。在特定情況下,可以通過輸入疊加態![]() 和

和![]() (

(![]() )來生成最大糾纏的貝爾態

)來生成最大糾纏的貝爾態![]() 、

、![]() 、

、![]() 和

和![]() 。在實驗中,四個貝爾態都被準確地生成了,如圖3g-3n。相應保真度分別為0.9034±0.0110,0.9634±0.0059,0.9578±0.0068和0.9382±0.0067,這證明了該門良好的糾纏能力。為了充分表征反設計的CNOT門,研究人員還進行了量子過程層析。通過實驗數據處理,進一步得到了CNOT門的量子過程保真度Fexp=0.9080±0.0030。

。在實驗中,四個貝爾態都被準確地生成了,如圖3g-3n。相應保真度分別為0.9034±0.0110,0.9634±0.0059,0.9578±0.0068和0.9382±0.0067,這證明了該門良好的糾纏能力。為了充分表征反設計的CNOT門,研究人員還進行了量子過程層析。通過實驗數據處理,進一步得到了CNOT門的量子過程保真度Fexp=0.9080±0.0030。

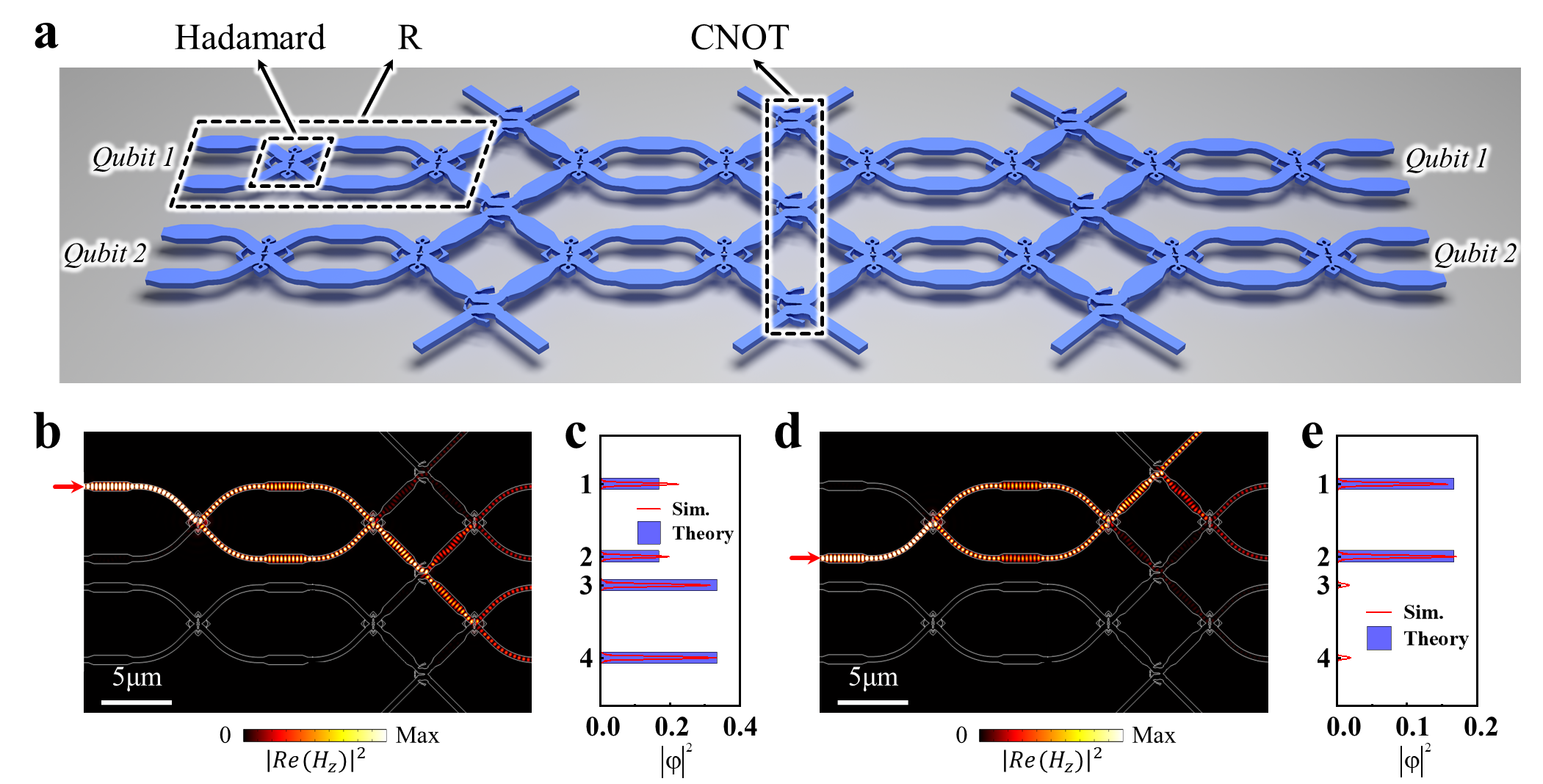

研究亮點之三:基于反設計方法的超緊湊光量子回路

量子門的主要應用之一是構建集成光量子回路,來實現任意的量子過程。因此,證明所設計的反設計量子門可以用于構建具有超緊湊尺寸的量子回路具有重要意義。如圖4a所示的示意圖,任意的兩量子比特量子回路可以由三個反設計的CNOT門和八個任意的R門組成。這樣一個量子回路的尺寸約為103 μm2。與以前的工作相比,尺寸縮小了4個數量級,從107μm2縮小到103 μm2。這意味著超過104個2量子比特量子回路可以集成到相同的區域。

圖4. 反設計超緊湊量子回路的方案。

為了測試所設計的超緊湊量子回路的功能,研究人員進行了單光子態演化的數值模擬。圖4b和圖4d展示了單光子態從第一個和第二個波導激發的概率幅的平方。從第一到第四個波導的輸出態的相應的概率幅平方標記為圖4c和圖4e中的紅線。同時,這四個波導的輸出疊加態的概率幅的平方的理論結果被標記為圖中的藍色矩形。比較這些結果,可以發現理論和數值模擬之間的一致性很好,這表明即使將量子回路集成到如此小的尺寸中,量子回路的功能也可以很好的被執行。

研究人員使用反設計方法在集成源的硅光子芯片上設計并制造了超緊湊的通用量子邏輯門。CNOT門和Hadamard門的尺寸分別只有8.32μm2(1.3μm×6.4μm)和1.69μm2(1.3μm×1.3μm),它們是目前報道的最小的光量子門。基于這些通用量子邏輯門,研究人員還設計了用于實現任意兩量子比特信息處理的硅光子量子回路。相比之前的量子光子回路,這個回路的尺寸縮小了4個數量級。這些超緊湊量子門和回路的高性能效率也已經得到了證明。這項工作為芯片集成的量子信息處理提供了新思路。

論文鏈接1:https://www.science.org/doi/10.1126/sciadv.adg6685

論文鏈接2:https://doi.org/10.1021/acsphotonics.1c01569

分享到: